题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

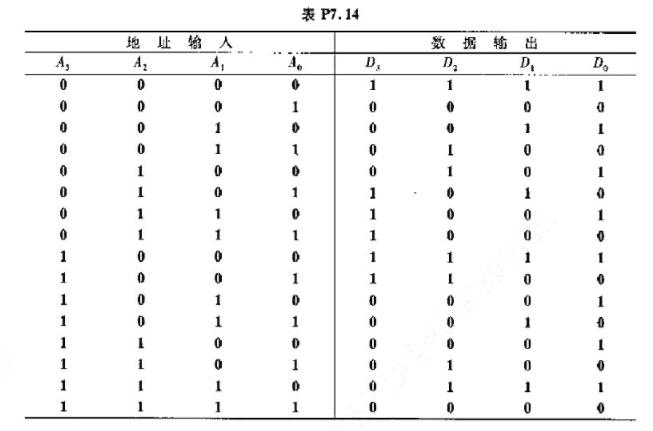

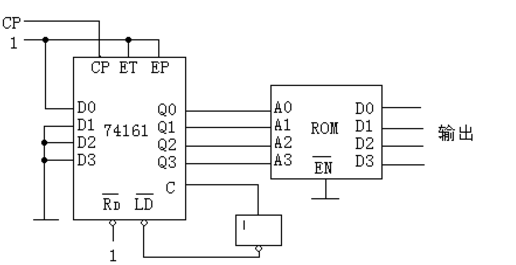

用ROM实现8路脉冲分配器。要求各路输出正脉冲的宽度为1μs。各路脉冲依次延迟一个时钟周期。画出实现电路图,说

明所用ROM的数据位宽m,地址位宽p,存储单元数目。写出各存储单元的地址和存储数据的表格。说明时钟CP的频率应为多少。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

明所用ROM的数据位宽m,地址位宽p,存储单元数目。写出各存储单元的地址和存储数据的表格。说明时钟CP的频率应为多少。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用ROM实现8路脉冲分配器。要求各路输出正脉冲的宽度为1μs…”相关的问题

更多“用ROM实现8路脉冲分配器。要求各路输出正脉冲的宽度为1μs…”相关的问题

A.STA=1.STB=DSTC=0

B.STA=1.STB=DSTC=D

C.STA=1.STB=0.STC=D

D.STA=DSTB=0.STC=D

号连续作用下D3、D2、D1、D0输出的电压波形,并说明它们和CP信号频率之比。

| 地址输入 | 数据输出 |

| A3A2A1A0 | D3D2D1D0 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 1 1 1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 0 1 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 1 0 0 0 0 0 1 0 0 1 0 0 0 0 1 0 1 0 0 0 1 1 1 0 0 0 0 |

由16×4位ROM和4位二进制加法计数器74LS161组成的脉冲分配电路如图7-13所示,ROM输入和输出关系如表7-4所示。试画出在CLK信号作用下D3、D2、D1、D0的波形。

表7-4 R0M输入和输出关系 | |||||||

| 地址输入 | 数据输出 | ||||||

| A3 | A2 | A1 | A0 | D3 | D2 | D1 | D0 |

| 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | 1 0 0 0 0 1 1 1 1 1 0 0 0 0 0 0 | 1 0 0 1 1 0 0 0 1 1 0 0 0 1 1 0 | 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 | 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 |

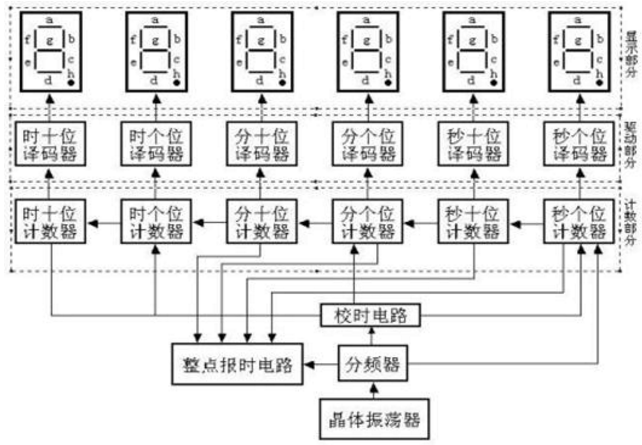

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

A.三相正(或负)触发脉冲依次间隔为120°,而每一相正、负触发脉冲间隔为180°。

B.为了保证电路起始工作时能两相同时导通,以及在感性负载和控制角较大时,仍能保持两相同时导通,与三相全控整流桥一样,要求采用双脉冲或宽脉冲触发。

C.为了保证输出电压对称可调,应保持触发脉冲与电源电压同步。

D.为了保证输出电压对称可调,应保持触发脉冲与电源电压同步。