题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

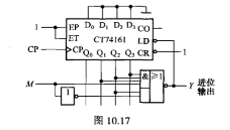

图10.17是可变进制计数器.试分析当控制变量M为1或0时,电路各为几进制计数器,并画出计数器的状

态转换图.

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图10.17是可变进制计数器.试分析当控制变量M为1或0时,…”相关的问题

更多“图10.17是可变进制计数器.试分析当控制变量M为1或0时,…”相关的问题

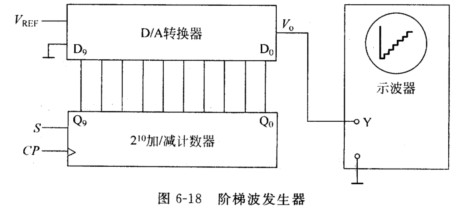

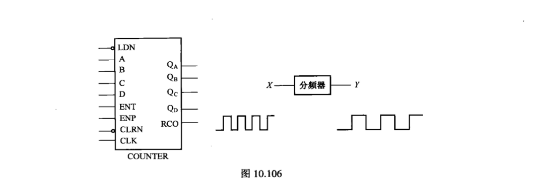

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

图8.2.1(a)所示为产生宽度等于1 2个CP周期的脉冲产生器,试选择MSI计数器设计控制电路,并画出电路的工作波形。

1.jpg)

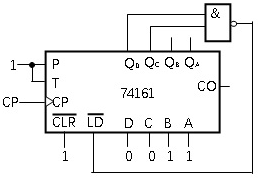

A.余3码编码的十进制加法计数器

B.循环码编码的九进制加法计数器

C.余3码编码的三进制加法计数器

D.循环码编码的二进制加法计数器

如图电路中,RS=1Ω,gm与US为定值,RL可变,已知当RL=1/2Ω时,RL上获得最大功率,且有PIImax=1/8W,试确定gm与US值。