题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

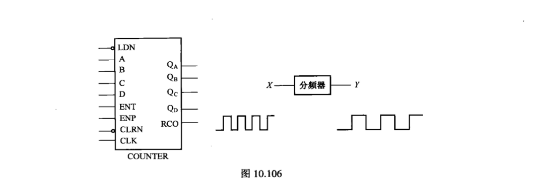

利用集成二进制计数器CT74163和必要的门电路,设计一个分频器.当输入X为1Hz方波时,输出Y为60Hz

方波(占空比为1).要求采用模10计数器和模6计数器串联设计.画出整个电路的逻辑电路连接图,并做出每一个CT74163器件的状态转移图.CT74163的逻辑符号如图10.106所示.

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“利用集成二进制计数器CT74163和必要的门电路,设计一个分…”相关的问题

更多“利用集成二进制计数器CT74163和必要的门电路,设计一个分…”相关的问题

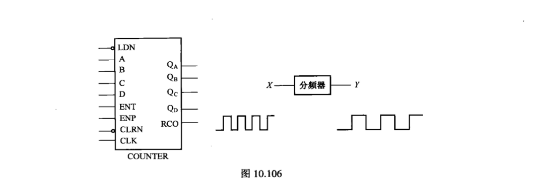

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

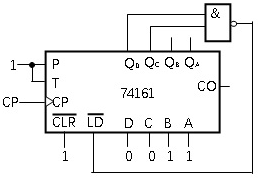

A.余3码编码的十进制加法计数器

B.循环码编码的九进制加法计数器

C.余3码编码的三进制加法计数器

D.循环码编码的二进制加法计数器

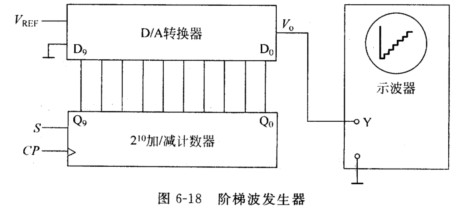

位二进制加法计数器CT74161和集成单稳态触发器CT74LS121组成如图P6.10(a)所示的电路.

(1)分析CT74161组成电路,画出转换状态图.

(2)估算CT74LS121组成电路的输出脉宽Tw值.

(3)设CP为方波(周期Td≥1ms),在图P6.10(b)中画出图P6.10(a)中u1、u0两点的工作波形.

A.ENP=1;ENT=0

B.ENP=1;ENT=1

C.ENP=0;ENT=1

D.ENP=0;ENT=0