题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

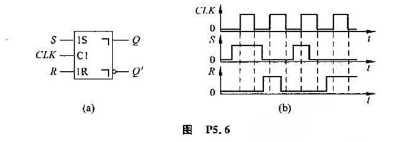

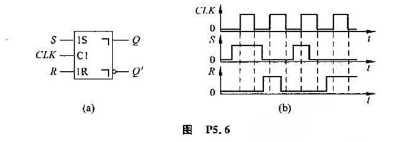

画出图P5.6(a)中脉冲触发SR触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入S、R的电压波形如

图P5.6(b)所示。设触发器的初始状态为Q=0。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图P5.6(b)所示。设触发器的初始状态为Q=0。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“画出图P5.6(a)中脉冲触发SR触发器输出端Q和Q'的电压…”相关的问题

更多“画出图P5.6(a)中脉冲触发SR触发器输出端Q和Q'的电压…”相关的问题

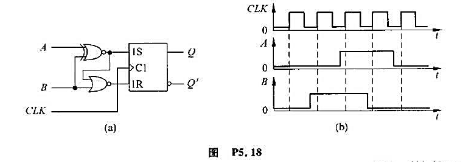

当CLK和A、B为图P5.18(b)给定电压波形时,Q端对应的电压波形。设触发器的初始状态为Q=0。

位二进制加法计数器CT74161和集成单稳态触发器CT74LS121组成如图P6.10(a)所示的电路.

(1)分析CT74161组成电路,画出转换状态图.

(2)估算CT74LS121组成电路的输出脉宽Tw值.

(3)设CP为方波(周期Td≥1ms),在图P6.10(b)中画出图P6.10(a)中u1、u0两点的工作波形.

时,向可控硅T送入触发脉冲,则输出电压uo的有效值为( )

时,向可控硅T送入触发脉冲,则输出电压uo的有效值为( )A.

B.

C.110V

D.220V

图8.2.1(a)所示为产生宽度等于1 2个CP周期的脉冲产生器,试选择MSI计数器设计控制电路,并画出电路的工作波形。

1.jpg)

两个单稳态触发器可以组成一个振荡器,且脉冲宽度和间歇宽度可以分别由定时元件RC设计,图(a)是MC14528单稳态的符号,图(b)是要求产生的振荡波形。已知tw=0.6RC试计算两个单稳态所用定时电容的电容值(用近似的标称值),并画出完整的电路图。

A.中断触发信号由单片机的P3.0引脚输入

B.中断触发方式选择位ET0可以实现电平触发方式或脉冲触发方式的选择

C.在电平触发时,高电平可引发IE0自动置位,CPU响应中断后IE0可自动清零

D.在脉冲触发时,下降沿引发IE0自动置位,CPU响应中断后IE0可自动清零

设集成运放的摆率SR=100V/μs,用它来放大脉冲信号。如果定义输出脉冲的上升沿为从0V变化到Vm所需的时间(Vm是脉冲幅度),请问:当脉冲幅度分别为5V、10V和15V时的脉冲上升沿为多少?如果要求3种幅度下的上升沿都不大于0.1μs,应当选用什么样的运放?