更多“若4位同步二进制加法计数器当前的状态是0111,下一个输入时…”相关的问题

更多“若4位同步二进制加法计数器当前的状态是0111,下一个输入时…”相关的问题

第2题

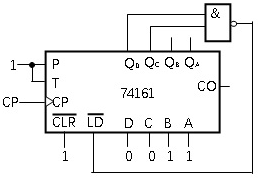

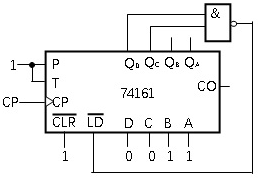

用4位二进制加法计数器74161构成的计数器电路如图所示,则对该计数器应用电路功能描述正确的是()。

A.余3码编码的十进制加法计数器

B.循环码编码的九进制加法计数器

C.余3码编码的三进制加法计数器

D.循环码编码的二进制加法计数器

第3题

对于集成计数器74LS161,如下描述正确的是()。

A.同步4位二进制计数器,具有同步清零功能

B.同步4位二进制计数器,具有异步清零功能

C.同步8421BCD十进制计数器,具有异步清零功能

第4题

试编子程序,返回16位二进制数中指定位段的零状态。已知: 入口参数:AX=16位二进制数; BL=高4位b1、低4位b0;

试编子程序,返回16位二进制数中指定位段的零状态。已知:

入口参数:AX=16位二进制数;

BL=高4位b1、低4位b0;

其中b1和b0分别为位段最高位编号和最低位的编号(15~0)。

出口参数:CE=0;

若指定位段为0,ZF=1,否则ZF=0。

注意:若b1小于b0,则不予处理,返回CF=1。

第5题

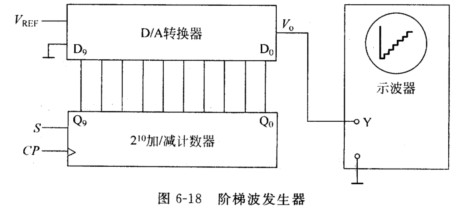

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

第6题

有一个十进制数加法运算系统,它利用4位二进制数加法器对一位8421BCD码进行加法运算.其操作过程如下:先将两个1位十进制数存入寄存器A和B,然后进行相加.如果和数等于或小于9,则运算结果正确;如果和数大于10,还需要对运算结果进行加6(0110)修正,这是因为用二进制数表示十进制数时,多余了6种状态.(1)请设计系统方框图;(2)请设计ASM流程图.

有一个十进制数加法运算系统,它利用4位二进制数加法器对一位8421BCD码进行加法运算.其操作过程如下:先将两个1位十进制数存入寄存器A和B,然后进行相加.如果和数等于或小于9,则运算结果正确;如果和数大于10,还需要对运算结果进行加6(0110)修正,这是因为用二进制数表示十进制数时,多余了6种状态.(1)请设计系统方框图;(2)请设计ASM流程图.

点击查看答案

第8题

位二进制加法计数器CT74161和集成单稳态触发器CT74LS121组成如图P6.10(a)所示的电路.(1)分析CT

位二进制加法计数器CT74161和集成单稳态触发器CT74LS121组成如图P6.10(a)所示的电路.(1)分析CT

点击查看答案

位二进制加法计数器CT74161和集成单稳态触发器CT74LS121组成如图P6.10(a)所示的电路.

(1)分析CT74161组成电路,画出转换状态图.

(2)估算CT74LS121组成电路的输出脉宽Tw值.

(3)设CP为方波(周期Td≥1ms),在图P6.10(b)中画出图P6.10(a)中u1、u0两点的工作波形.

第10题

试利用两片4位二进制并行加法器741S283和必要的门电路.组成1位二-是进制加法器电路.(根据二-十进制数的加法运算规则,当两数之和小于、等于9(1001)时,相加的结果和按二进制数相加所得到的结果一样.当两数之和大于9(即等于1010~111)时,则应在按二进制数相加的结果上加6(0110),这样就以给出进位信号,同时得到一个小于9的和.)

试利用两片4位二进制并行加法器741S283和必要的门电路.组成1位二-是进制加法器电路.(根据二-十进制数的加法运算规则,当两数之和小于、等于9(1001)时,相加的结果和按二进制数相加所得到的结果一样.当两数之和大于9(即等于1010~111)时,则应在按二进制数相加的结果上加6(0110),这样就以给出进位信号,同时得到一个小于9的和.)

点击查看答案

第11题

设某数字传输系统采用连贯式插入法实现顿同步.插入的帧标记为7位巴克码。 (I)试画出帧同步码识别器原理框图; (2)若输入二进制序列为0101110011100100.试画出顿同步码识别器的输出波形设判决门限电平为4.5,且设备移位寄存器初始状态均为零 (3)若码元错误概率为P2,识别器判决门限电平为4.5,试求该识别器的假同步概率。

设某数字传输系统采用连贯式插入法实现顿同步.插入的帧标记为7位巴克码。 (I)试画出帧同步码识别器原理框图; (2)若输入二进制序列为0101110011100100.试画出顿同步码识别器的输出波形设判决门限电平为4.5,且设备移位寄存器初始状态均为零 (3)若码元错误概率为P2,识别器判决门限电平为4.5,试求该识别器的假同步概率。

点击查看答案

如果结果不匹配,请

如果结果不匹配,请