更多“在TTL电路中,能实现“线与”逻辑的是()。”相关的问题

更多“在TTL电路中,能实现“线与”逻辑的是()。”相关的问题

第1题

图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的

图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的输出各是什么? (1)两个电路均为CMOS门;

1.jpg) (2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

(2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

第3题

TTL集成施密特触发器CTll32的逻辑符号和vI一vO曲线如图9.6.1(a)所示,图(b)为CTll32组成的电路。

TTL集成施密特触发器CTll32的逻辑符号和vI一vO曲线如图9.6.1(a)所示,图(b)为CTll32组成的电路。 (1)说明电路具有什么功能。 (2)定性画出VA,VO的波形。 (3)若R=10 kΩ,C=0.01μF,计算工作周期。

.jpg)

第7题

基于课本上所示的PLA分别实现表(1)、(2)给出的2位-4线译码器电路。 表(1) 2位-4线译码(正逻辑输出)

基于课本上所示的PLA分别实现表(1)、(2)给出的2位-4线译码器电路。

| 表(1) 2位-4线译码(正逻辑输出) | |||||||

| S1 | bar{S_2} | A1 | A0 | Y0 | Y1 | Y2 | Y3 |

| 1 1 1 1 0 varphi | 0 0 0 0 varphi 1 | 0 0 1 1 varphi varphi | 0 1 0 1 varphi varphi | 1 0 0 0 0 0 | 0 1 0 0 0 0 | 0 0 1 0 0 0 | 0 0 0 1 0 0 |

| 表(2) 2位-4线译码(负逻辑输出) | |||||||

| S1 | bar{S_2} | A1 | A0 | bar{Y_0} | bar{Y_1} | bar{Y_2} | bar{Y_3} |

| 1 1 1 1 0 varphi | 0 0 0 0 varphi 1 | 0 0 1 1 varphi varphi | 0 1 0 1 varphi varphi | 0 1 1 1 1 1 | 1 0 1 1 1 1 | 1 1 0 1 1 1 | 1 1 1 0 1 1 |

第10题

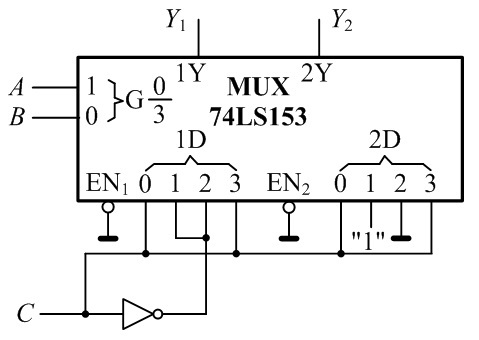

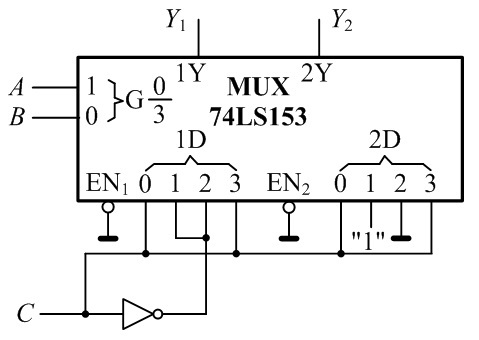

用双4选1数据选择器74LS153实现的逻辑电路如下图所示,试分析该电路的逻辑功能,下列说法正确的是()。

A.该电路实现全加器的逻辑功能,Y1为和的输出,Y2为进位输出

B.该电路实现一致性判别的逻辑功能,Y1是判别为一致时的输出,Y2为不一致的输出

C.该电路实现奇偶校验的逻辑功能,Y1为奇数输出,Y2为偶数输出

D.该电路实现全减器的逻辑功能,Y1为差的输出,Y2为借位输出

第11题

设有一个16位定点补码运算器,序号0为最低位,能实现下述功能: A±X→A X×Q→A//Q(高位积在

设有一个16位定点补码运算器,序号0为最低位,能实现下述功能: A±X→A X×Q→A//Q(高位积在A中) A÷x→Q(商在Q中) (1)列出实现上述功能的控制信号; (2)画出全加器第5位和A、Q寄存器第5位的输入电路。

如果结果不匹配,请

如果结果不匹配,请

)

)